Different types of Shift Register

The shift register is a type of sequential circuit, where the data bits can be stored and can be transferred. Shift registers are constructed using flip-flops, so it is an application of flip-flops.

Since flip-flop is a single-bit storage element, multiple flip-flops can be used to store multiple bits of data. For example, to store n-bit data, n number of flip-flops are to be connected in series.

A register is nothing but a group of flip-flops connected together to store multiple bits of data. Upon the application of the clock pulse, the stored data can be moved from one flip-flop to another or in/out of the registers. Such a device is called a shift register.

D flip-flops are used in the shift register. It is because the D flip-flop can perform the operation of moving the data from the input to the output during the application of a clock pulse.

Types of Shift Register

The data bits can be shifted serially from left to right and from right to left or the data can be rotated within the shift registers or the serially shifted data can be taken as parallel output and so on. On the basis of the movement of data in a register, there are 6 types of shift registers.

- Serial In Serial Out Shift register

- Serial In Parallel Out Shift register

- Parallel In Serial Out shift register

- Parallel In Parallel Out shift register

- Bidirectional shift register

- Universal shift register

Let us look at each of the above types in detail.

Serial-In Serial-Out(SISO) Shift Register

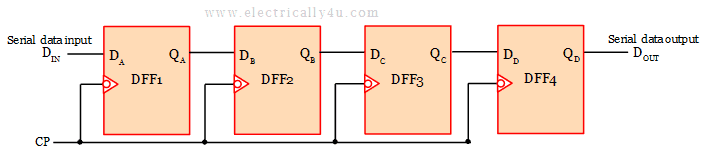

It is one of the simplest of all the shift registers. The Serial In Serial Out shift register is constructed with four flip-flops. It has one input, one output and a clock pulse input. The block diagram is shown below.

Here, the data is inserted at the input bit by bit. For each clock pulse, the data bit is shifted from one flip-flop to the next flip-flop. At the output side, the inserted data will be received bit by bit for each clock pulse.

Since the inserted data and the received data are done in a bit-by-bit fashion, this register is known as the Serial in Serial out shift register.

Operation of Seiral In Serial Out Shift register

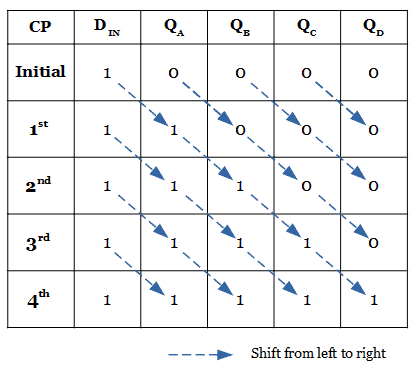

The below table summarizes the operation of the Serial In Serial Out shift register, where the shift is done from left to right. Initially, the output of all the flip-flops is assumed to be logic 0. Consider the data at the input terminal DIN be 1.

During the first clock pulse, logic 1 at the input DIN is shifted to the output of the first flip-flop QA. Similarly, the data input at other flip-flops is also shifted by one position. It is shown in the third row of the above table.

During the second clock pulse, logic 1 at the inputs of the first and second flip-flop are shifted by one position. The logic 0 input at the other inputs of the flip-flop is also shifted by one position, which is shown in the fourth row of the above table.

This shifting operation continues for each clock pulse. At the end of the fourth clock pulse, the inserted data bit ‘1’ will be received at the output terminal DOUT.

It is also possible to shift the data from right to left by following the same procedure.

Serial-In Parallel-Out(SIPO) shift register

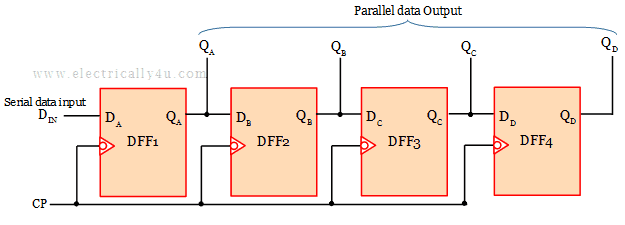

In the Serial-in Parallel-out shift register, the data is inserted bit by bit serially. The data input at all the flip-flops is shifted by one position for every clock pulse. The output at each flip-flop can be taken out in a parallel fashion. The circuit of the Serial-in Parallel-out shift register is shown in the figure below.

During the clock pulse, the D input of each flip-flop is shifted to the Q output. The Q outputs of all the flip-flops are tapped separately. Thus the parallel output data(QAQBQCQD) will have the bit from each individual register. The Serial-in Parallel-out shift register is mainly used for communication purposes where the serial input data in converted into parallel output data.

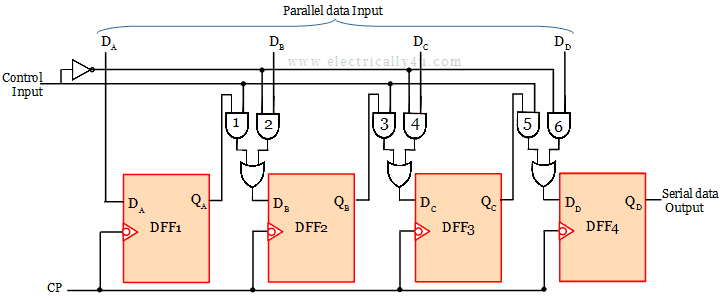

Parallel-In Serial-Out(PISO) shift register

It is just opposite to the one we discussed above. In the parallel In Serial Out Shift register, the data is inserted or loaded into each register in parallel and the inserted data is received serially at the output.

Here the data is to be loaded at the input of each flip-flop. At the same time, while applying the clock pulse, the data at the output of each flip-flop will be moved to the input of the next flip-flop.

So to avoid conflicts between the loaded data and the shifted data at the inputs, the control input is added in this shift register. The Parallel In Serial Out Shift register is shown in the below diagram.

If the control input is 0, the AND gates 1, 3, 5 will be disabled and gates 2, 4, 6 will be enabled. It will make the parallel data at the inputs(DADBDCDD) to get stored in the respective flip-flops. For loading the parallel input data, a clock pulse is not required.

When the control input is 1, it will enable the AND gates 1, 3, 5 and the gates 2, 4, 6 will get disabled. During this time, when a clock pulse is applied, the data bit at the input of each flip-flop is shifted to its output.

Thus in the Parallel In Serial Out Shift register, the data is loaded parallelly into the individual registers and upon the application of each clock pulse, the data is shifted serially. The serial output is obtained from the Q output of the last flip-flop.

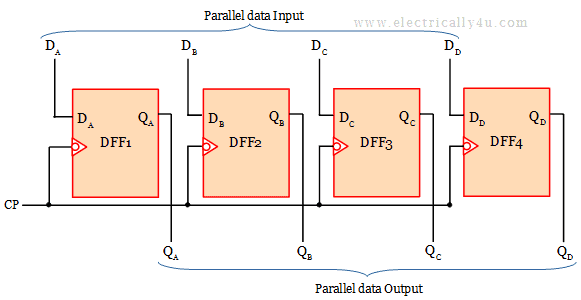

Parallel-In Parallel-Out(PIPO) shift register

In Parallel-in Parallel-out shift register(PIPO), the input data is loaded parallelly into each individual register and the output is received from each flip-flop output.

It is used for the temporary storage of data or as time delay devices. The block diagram of the Parallel-in Parallel-out shift register is shown below.

D flip-flop is used for the construction of the Parallel-in Parallel-out shift register. The four-bit data is loaded at the input of four flip-flops. When a clock pulse is applied, the loaded data is shifted to the output of the flip-flop, which is tapped out for measurements. A single clock pulse will load the data and unload the data.

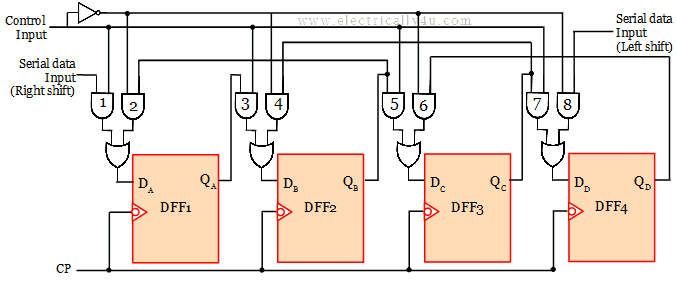

Bidirectional Shift Register

The Serial In Serial Out shift register(SISO) will either shift the data from left to right or from right to left. But the bidirectional shift register will be capable of shifting the data in both directions based on the selected mode or control input.

If the control input is given logic 0, it will disable AND gates 1, 3, 5, 7 and enable gates 2, 4, 6,8. The enabled AND gates will make the data be shifted from right to left. The following figure shows the block diagram of the bidirectional shift register.

When the control input is given as Logic 1, the AND gates 1, 3, 5, 7 will be enabled and gates 2, 4, 6, 8 will be disabled. This will shift the data from left to right.

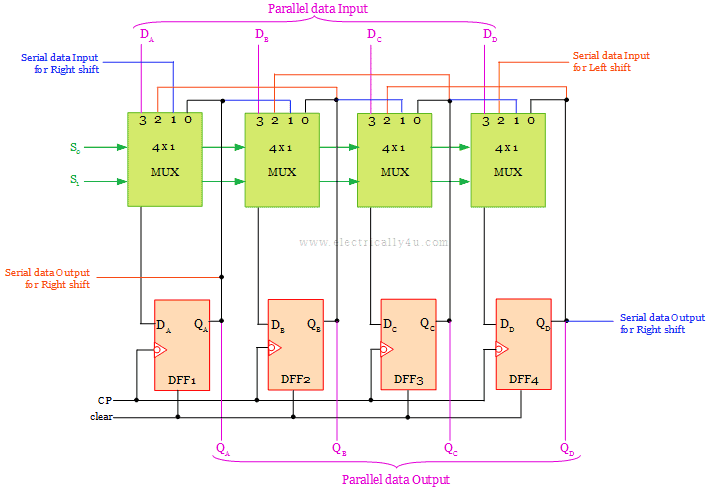

Universal Shift Register

It is a multi-function shift register, which can perform any type of data bit movement across the registers. The data can be loaded and it can be retrieved in either serial or in a parallel way.

Thus it can perform any type of operation like serial to serial operation(both shift left and shift right), parallel to parallel conversion, serial to parallel and parallel to serial conversion. Hence the name Universal shift register.

The block diagram of the universal shift register is shown below.

As you can see from the block diagram, it has four D flip-flops and four multiplexers. All the multiplexers have the same select lines(S0 and S1, shown in green color). The select line is used to select the mode of the shift register.

Depending upon the selection line input, the shift register operates. If S0S1 = 00, there will not be any change in the shift register output. If S0S1 = 01, then serial shift right operation(shown in blue color) will take place.

When the selection input S0S1 = 10, the data will be shifted left, as shown in red color. When S0S1 = 11, the data will be loaded parallelly through the inputs DADBDCDD and retrieved from each flip-flop at QAQBQCQD(shown in pink color).

Universal shift registers are used in the arithmetic operation of binary numbers where the shifting of data is necessary.

Related Posts